Overview

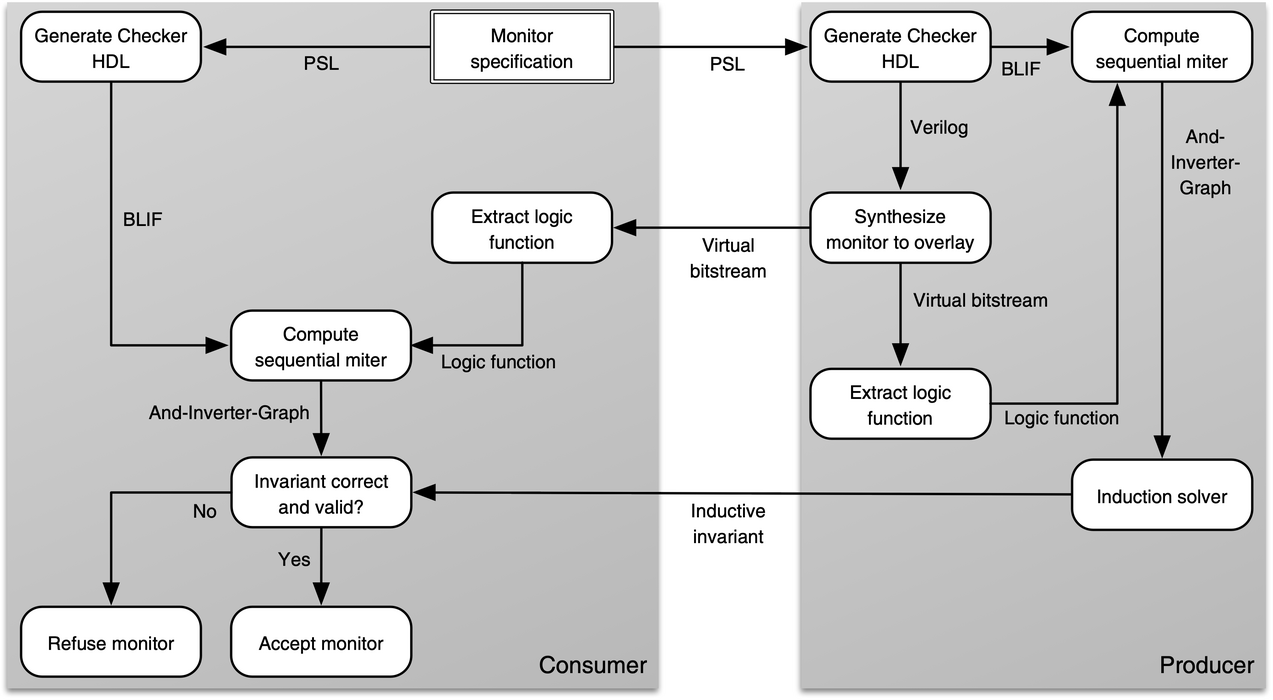

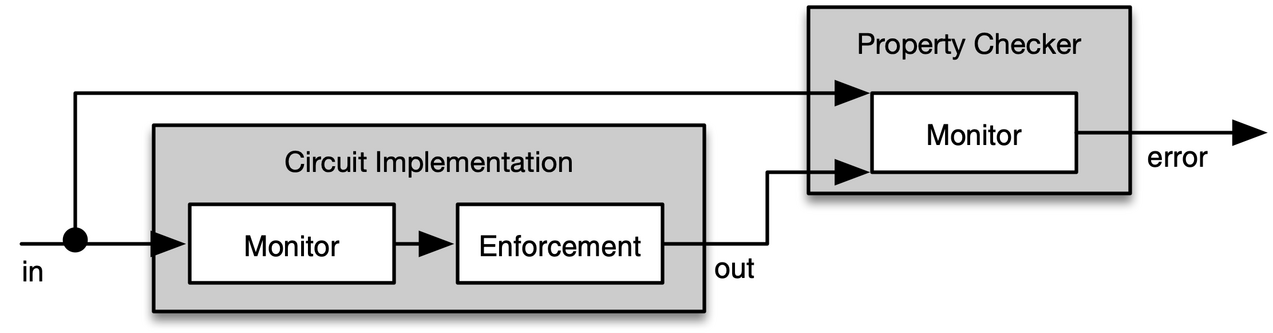

The concept of Proof-Carrying Code (PCC) and Hardware (PCH) is defined in a two-party contract work scenario, where a Consumer creates a functional specification along with corresponding properties (functional or non-functional) that the resulting binary should or should not exhibit. A Producer is then tasked with creating such a binary together with a proof of conformance to the desired properties, resulting in a Proof-Carrying Binary that is sent to the Consumer, who then validates the proof and can afterwards know beyond any doubt if the received binary is trustworthy or not. For further details please read the description of subproject B4.

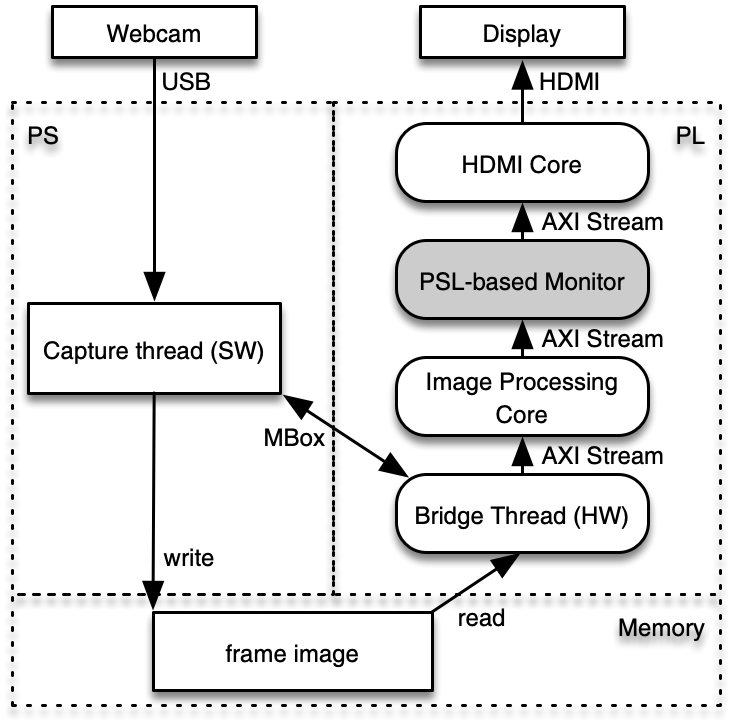

In the case of the Proof-Carrying Hardware Demonstrator, the target platform is a reconfigurable hardware device, like an FPGA, or a system-on-chip that includes programmable logic, and the binaries are thus configuration bitstreams for such programmable logic. The Proof-Carrying Hardware Demonstrator is a collection of software tools, scripts and hardware modules that demonstrate the PCH tool flow and show the proof-carrying hardware service exchange between a provider and an OTF service provider.

Flow

Contact

If you have any questions regarding the PCH demonstrator, please contact the research staff from Subproject B4.